### WIP CONTROL AND CALIBRATION IN A WAFER FAB

Zhugen Zhou Oliver Rose

Computer Science Department University of Federal Armed Forces Munich 85577 Neubiberg, GERMANY

#### **ABSTRACT**

In this paper, a priority matrix table is used to assign priority to lots according to due date and workload information with the objective to keep lots going through the fab at the right pace to maintain WIP balance. Besides that, a WIP calibration method is proposed to recover WIP balance due to events such as unpredictable tool failure. The simulation results demonstrate that the proposed priority matrix table achieves a better WIP balance than FIFO (first in first out) and ODD (operation due date), and the WIP calibration method is able to correct for the WIP imbalance.

## 1 INTRODUCTION

Typical wafer fabrication facilities (wafer fabs) contain hundreds of production equipments and dozens kind of wafer products. Each kind of product has a unique technologic process flow which includes hundreds of processing steps. Wafer fabrication is considered as one of the most complex manufacturing process because of re-entrant processing flow, batch processing, sequence dependent setups, unpredictable tool failure and so on, which differentiate wafer fab from other traditional flow shop or job shop.

Work-in-process (WIP) is an important performance indicator in a wafer fab. Due to those characteristics mentioned above, WIP imbalance occurs frequently which represents in two ways. On one hand, WIP distributes intensively in some operations while some operations have a low WIP. On the other hand, some work-centers are overloaded while some work-centers are starved. The breakdown of overloaded work-centers could block the manufacturing process and cause excessive WIP level in the fab. This WIP imbalance has great impact on cycle time and on-time delivery. Therefore, it is essential that an effective WIP control policy can be applied to smooth the WIP flow and maintain a low WIP level in the fab.

During past years, a large number of WIP control approaches have been developed by academic and industrial researchers such as Minimum Inventory Variability Scheduler (MIVS) proposed by Li et al. (1996) and global Line Balance (LB) algorithm proposed by Dabbas and Fowler (2003). Both MIVS and LB consider WIP balance from the viewpoint of operations, while some researchers addressed WIP balance from the viewpoint of work-centers like Zhou and Rose (2010). Although different WIP control approaches look at WIP balance at different viewpoint, they all have the same objective to make sure that the fab runs in a smooth way and each lot goes through the fab at the right pace.

Although huge effort has been made to maintain WIP balance, WIP fluctuation phenomena occurs frequently. In case WIP abnormal situation takes place, an effective way to monitor and calibrate is vital to avoid WIP imbalance getting worse. The most popular way is to predefine a target WIP level for the operation or work-center (Li et al. 1996; Leachman et al. 2002; Kuo et al. 2008). If the actual WIP level is higher than the target WIP level, which means the operation or work-center has a high possibility to get congestion and the upstream is better to stop feeding. If the actual WIP level is lower than the target WIP level, which means the operation or work-center is starved and upstream needs to feed more. The accura-

cy of such WIP correction method lies in an appropriate target WIP level. However, for a customeroriented company lot release rate is changing all the time due to frequent change of customer orders. In this case, the fab is running at different capacity loading daily, weekly and monthly. The target WIP level needs to be updated accordingly. Therefore, it is extreme difficult to determine and apply an appropriate target WIP level for the operation or work-center.

In this paper, we introduce a priority matrix table which prioritizes lots according to the due date and workload information. Our goal is to keep the lots going through the fab smoothly and at the right pace to achieve WIP balance. Instead of predefining target WIP level maintaining throughput is used as a trigger event to monitor WIP imbalance. When the fab is running in a stable state, in case the throughput rate decreases suddenly, which means more and more lots will remain in the fab and the WIP will keep building up. In such circumstances, the WIP imbalance definitely occurs somewhere in the fab and represents as WIP distributes intensively in some operations. Therefore, analysis of WIP position for operation is very necessary to smooth the manufacturing process.

This paper is organized as follows. In Section two, the proposed priority matrix table and WIP calibration approach will be described in detail. Then the simulation results and performance measures will be analyzed in Section three. Section four gives the conclusion.

### 2 PRIORITY MATRIX TABLE AND WIP CALIBRATION APPROACH

# 2.1 Priority Matrix Table

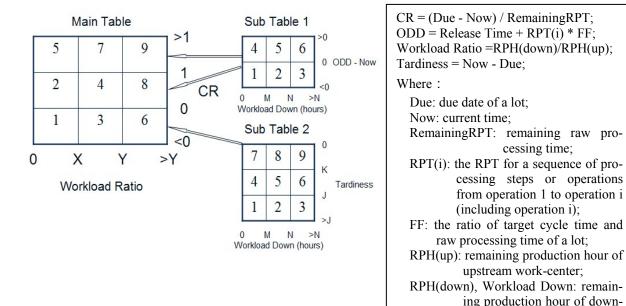

Previous study addressed simultaneously optimizing WIP balance and on-time delivery needs to focus on workload information of work-center, and the due date information of lot as well. This study proposes a priority matrix table which employs critical ratio (CR), workload and operation due date (ODD) (Baker and Bertrand 1981), with the purpose to keep lots progressing smoothly toward on-time completion without serious WIP fluctuation.

The priority table includes a main table and a sub table. The main table ranks the dispatching sequence by nine priorities according to the CR value of lot and workload ratio between downstream and upstream work-center. As shown in Figure 1, the CR and workload ratio are divided into 3 levels which leads to a combination of nine priorities. The CR value larger than 1 means the lot is ahead of schedule, between 0 and 1 represents the lot falls behind schedule and gets close to final due date, less than 0 demonstrates the lot is tardy. The workload ratio is the ratio between the remaining production hours of downstream and upstream work-center. The larger the workload ratio is, the lower priority the lot has. Obviously, the tardy lot has higher priority than the non-tardy lot, and the lot which is heading toward a work-center with low workload has higher priority than the lot which is heading toward a high loaded work-center. However, the compromise has to be considered between WIP balance and due date control, e.g. we would rather push an on schedule lot to downstream with less workload instead of push a tardy lot to high loaded downstream, which is the case of priority 5 and 6.

In some cases, more than one lot has the same priority in the main table. Therefore, two sub tables are used to subdivide priority in a granularity level. Sub table 1 is used for the case of CR larger than 0, which denotes the lot is still on schedule. In sub table 1, whether the lot is late for its operation due date is used to divide priorities into two levels, and the remaining production hours of downstream work-center is divided into three levels. As a result, there are six priorities in sub table 1. Each operation has its own operation due date, the lot late for its operations due date has a higher priority than the lot ahead of its operation due date. With respect to sub table 2, it focuses on the tardy lot case (CR less than 0). Three tardy levels and three levels of remaining production hours of downstream work-center lead to nine priorities in sub table 2. The more tardy the lot is, the more urgent the lot is. In the main table and sub table, less value represents higher priority, e.g. priority 1 is higher than priority 2. The lots in the queue are sequenced layer by layer according to the following:

• Priority(main table) -> Priority(sub table) -> ODD

If lots have the same priority from the current rule, then the next rule is used to distinguish until ODD is applied as the final rule, e.g. if lots have the same priority from main table, then the priority from sub table is used.

Figure 1: Priority main table and sub table

stream work-center:

In this study, the workload ratio levels X and Y from the main table are defined as 2 and 5, respectively. These values come from the model with FIFO dispatching. In sub table 1 and 2, the workload of downstream levels M and N are defined as one shift 8 hours and two shifts 16 hours, respectively. The tardy levels K and J are defined as 12 hours and 24 hours, respectively.

## 2.2 WIP Calibration Approach

When the fab is running in a steady state, the ideal WIP curve should evolve smoothly without increasing dramatically or fluctuating seriously. In reality, due to the characteristics of wafer fab, WIP imbalance occurs inevitably anywhere in the fab. In order to detect and correct for the WIP imbalance, a WIP abnormity monitor and calibration approach are proposed. In contrast to the traditional WIP abnormity monitor approach such as predefined target WIP level for operation or work-center, maintaining the throughput rate is applied as a trigger event to monitor WIP imbalance. In case the throughput rate decreases suddenly and is less than the release rate, which means more and more lots remain in the fab, the WIP will build up. WIP imbalance definitely happens somewhere in the fab, which represents as WIP distributes intensively in some operations. Hence, using WIP position analysis for operations to determine which high WIP operations should be pushed to balance the low WIP operations is very essential.

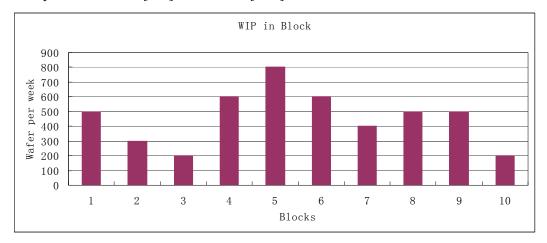

## 2.2.1 WIP in Block

Each lot's process flow can be divided into B blocks. Blocks correspond to a logical separation that allows having intermediate controls on lot manufacturing. In this study the model presented in the following section, average 30 process steps (one mask layer) form a block, which is provided by the experienced

industrial engineers. In practice, each block has an output goal for the next block to balance the WIP. Due to the computational and algorithm limitation, the exact output goal of each block is not defined in this study, which is also consistent with that no target WIP level is specified for the operation or work-center. As presented in Figure 2, total WIP[this] means the total WIP level of current block, and total WIP[next] means the total WIP level of next block. If the total WIP of current block is higher than the total WIP of next block, which represents the need of pushing WIP from current block to next block to maintain the throughput. Otherwise, the WIP builds up in current block. The following is three priorities of lot from Figure 2. For instance, the lots in Block 5 get higher priority than the lots in Block 4.

- Priority 1: If Total WIP[this] > Total WIP[next]

- Priority 2: If Total WIP[this] == Total WIP[next]

- Priority 3: If Total WIP[this] < Total WIP[next]

Figure 2: WIP in block

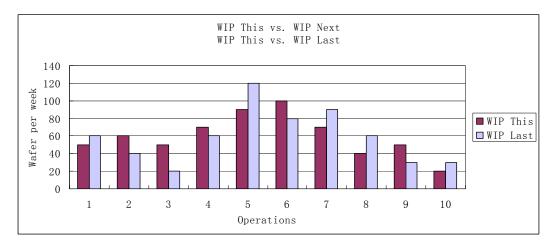

## 2.2.2 WIP Position Analysis of Operation

Each block includes dozens of operation steps. After determining which block should push the WIP to balance the downstream block, the next step is to balance the WIP inside the block to ensure the throughput. Figure 3 demonstrates an example of the WIP position analysis of operation. This WIP quantity histogram presents a visual picture of WIP balance. The WIP[this] is the current WIP level of operation i, the WIP[next] is the current WIP level of next downstream operation i+1, the WIP[last] is the average historical WIP level of operation i during the last 'X' hours. Instead of predefining a target WIP level for the operation like MIVS, through comparison between the WIP[this] and WIP[next], WIP[this] and WIP[last], e.g. operation 2 has more WIP than operation 3, and the WIP is increasing compared to its average historical WIP level. Hence, the WIP of operation 2 should be pushed to operation 3 immediately in case it accumulates to starve operation 3. The following is four priorities of lot from Figure 3.

- Priority 1: If WIP[this] > WIP[next] and WIP[this] > WIP[last]

- Priority 2: If WIP[this] > WIP[next] and WIP[this] <= WIP[last]

- Priority 3: If WIP[this] <= WIP[next] and WIP[this] > WIP[last]

- Priority 4: If WIP[this] <= WIP[next] and WIP[this] <= WIP[last]

#### 2.2.3 Balance Work-Center

Balancing WIP for operation ensures throughput for the block, thus achieving balance for block. However, due to the reentrant nature of wafer fab, the same work-center can perform different operations. Achieving WIP balance for operations does not mean WIP balance for work-center. The lots acquiring priority

from block and operation analysis above may have the same priority. Here Least Work at Next Queue (LWNQ) is applied to balance the WIP of work-center. The lot heading toward a work-center with less workload has high priority than the lot heading toward a high loaded work-center.

Figure 3: WIP position analysis of operation

#### 2.2.4 Reschedule Lots

In case the WIP calibration approach is applied to correct for WIP imbalance, the lots queuing in the work-center are re-sequenced according to the following:

• Priority(block) -> Priority(operation) -> LWNQ -> ODD

If lots have the same priority from the current rule, then the next rule is used to distinguish until ODD is applied as the final rule, e.g. if lots have the same priority from Block (Figure 2), then the priority from operation (Figure 3) is used to differentiate.

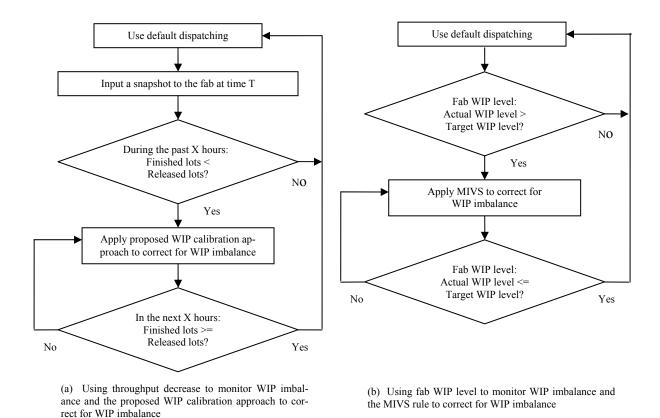

### 2.2.5 Monitor and Calibrate WIP Imbalance

Different from the traditional approach such as setting a target WIP level for the operation or work-center to monitor WIP imbalance occurrence, maintaining throughput is used as a trigger event in this study. In case the throughput decreases, the manufacturing process is blocked somewhere in the fab. It represents as excessive WIP accumulates in some Blocks which interrupts the WIP flow. For this reason, the lots are rescheduled according to the priority described in Section 2.2.4. The purpose is to make sure (1)WIP balance is inside the congestion Block; (2) the congestion Block pushes WIP to downstream Block to ensure throughput. Figure 4(a) presents this procedure to correct for WIP imbalance. We will explain why the proposed WIP calibration approach works in Section 3.3.

The contribution of this study is to propose a WIP calibration approach without applying target WIP level. In order to compare with the one applying target WIP level to achieve WIP balance, another procedure using total WIP level for the fab as trigger event and applying MIVS to rectify WIP imbalance are proposed and showed in Figure 4(b). In case the actual WIP level of the fab exceeds the target WIP level, MIVS is applied to minimize the difference between the instantaneous WIP and target WIP. The historical average WIP level for each operation from FIFO is used as target WIP level for MIVS in this study.

Figure 4: Two different methods to monitor and calibrate WIP imbalance

## 2.3 Simulation Model

The small wafer fab dataset MIMAC6 from Measurement and Improvement of MAnufacturing Capacities (MIMAC) is used to test our ideas. We refer the interested reader to Fowler and Robinson (1995) for details. MIMAC6 is a typical complex wafer fab model including:

- 9 products, 9 process flows, maximum 355 process steps.

- 24 wafers in a lot. 2777 lots are released per year under fab loading of 100%. All lots have the same priority of 1 when they are released in the fab.

- 104 tool groups, 228 tools. 46 single processing tool groups, 58 batching processing tool groups.

- Sequence dependent setup, rework, MTTR (mean time to repair), and MTBF (mean time between failures) of tool group.

#### 3 SIMULATION RESULTS AND PERFORMANCE ANALYSIS

We conducted the simulation with Factory eXplorer from WWK (Wright Williams & Kelly). The simulation length of MIMAC6 was carried out for 72 weeks. The first 24 weeks were considered as warm-up periods, and not taken into account for statistics. The fab capacity loading was set to 95%, which means the bottleneck work-center of the fab is driven to 95% utilization. The target due date flow factor was set to 2.0, this is a reasonable value because according to the fab running in the reign of FIFO, the percent tardy lots is 78%. If the target due date flow factor is too tight like 1.8, 100% of the lots will be tardy. If too loose like 2.2, only 23% of the lots will be tardy.

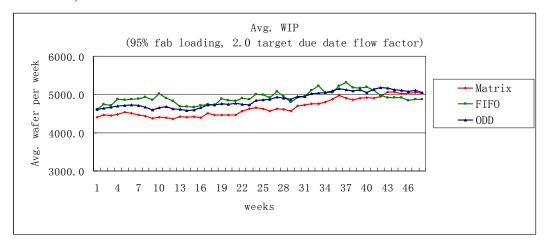

## 3.1 Priority Matrix Table

First of all, we compare the WIP curve of our proposed priority matrix table with in the case of FIFO and ODD. Figure 5 shows the three different WIP curves in 48 weeks. Apparently, the WIP performance of matrix table outperforms FIFO and ODD cases since it is lower and flatter than FIFO and ODD, which demonstrates the matrix table succeeds in scheduling lots in a more balance way instead of causing serious WIP fluctuation like FIFO. It also tells us that the matrix table helps to reduce WIP variation since it does not jump oftentimes. The WIP curve of the matrix table has a similar trend like ODD case. However, it is not as smooth as the ODD case. Begin from the 30th weeks, the WIP of matrix table keeps climbing, then it stays around 5000 wafers level. The reason is the tardy lots and the continuous arrival of fresh lots. According to the matrix table, the tardy lots get the higher priority than the new lots which are still in their early operation. In addition, the work-centers have breakdown. The consequence is the fresh lots can not be processed until the tardy lots leave the queue. Hence, the WIP builds up due to the continuous arrival of fresh lots. After the 37th week, the WIP goes down relatively. It also tells us that if the fab is running with considerable tardy lots, only focusing on due date control could lead to excessive WIP, because speeding up the tardy lot takes the cost of longer waiting time of other fresh lots. In case critical work-center has a failure, the fab state becomes difficult to control.

Figure 5: WIP evolution curve comparison among three different rules

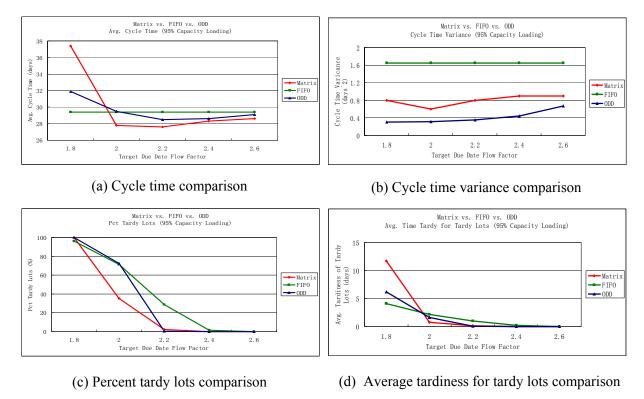

Secondary, the average cycle time, cycle time variance, percent tardy lots and average tardiness of tardy lots are considered as major performance measures. The target due date flow factor is ranging from 1.8 to 2.6 in steps of 0.2. We take a close look at how these four performance measures change corresponding to the target due date flow factor change. Figure 6 shows the results. We observe that the matrix table has a sudden performance degradation if the target due date is tight. Figure 6(a) shows that the average cycle time of the matrix table is considerable compared with FIFO and ODD at due date flow factor 1.8. With this tight due date, 100% of lots are tardy not only for the matrix table but also for FIFO and ODD cases. In this case, during warm-up periods, the lots in the middle operations are already tardy. The matrix table assigns high priority to those tardy lots to speed them up. Hence, the new arrival lots or the lots in the early operations get blocked. As time goes by, more and more lots become tardy. The lots in the early operations can not be processed and become tardy too. The matrix table only focuses on the tardy lots instead of new arrival lots. The consequence is the fab is running with large number of tardy lots. The throughput decreases due to overemphasizing due date control. The WIP keeps building up because of decreased throughput and continuous arrival of new lots, which causes considerable cycle time. It indicates again that overemphasized due date control could lead to high WIP level. The matrix table is not suitable for the case that 100% of lots are tardy under high fab capacity loading because of sudden performance degradation. With regard to the medium and loose target due date, the matrix table is superior over FIFO and ODD considering average cycle time and on time delivery. With respect to the cycle time

variance, the matrix table provides a mechanism to ensure lots go through the fab at the right pace and gets better performance than FIFO. However, it is outperformed by ODD.

Figure 6: Four performance measures comparison among three rules with difference target due date flow factors

## 3.2 Proposed WIP Calibration Approach

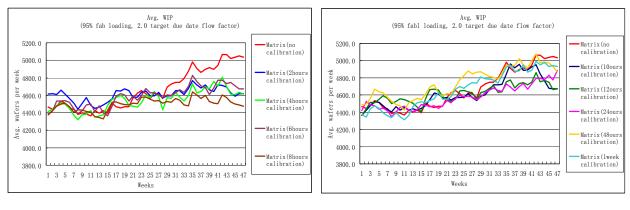

From Figure 5, we observe that from a global viewpoint the matrix table achieves more WIP balance than FIFO and ODD with the medial target due date. From a local viewpoint, the WIP curve of matrix table still has WIP imbalance such as the WIP keeps climbing from 30th weeks. One of the objectives of this study is to make sure the WIP go back to the right track. In case the throughput decreases, the WIP calibration approach is applied to calibrate the WIP abnormality and avoid WIP building up gradually.

Figure 7 shows the WIP differences between using matrix table with and without calibration. Figure 7(a) represents the calibration is applied every 2, 4, 6 and 8 hours, and the WIP calibration approach succeeds in preventing WIP from climbing from the 30th weeks. It seems that the WIP calibration with eight hours interval could achieve the best WIP curve. The WIP curve with calibration behaves smoothly, which implies the WIP calibration approach captures the WIP imbalance phenomenon and balance the block, operation and work-center simultaneously. Additionally, the smooth WIP curve also represents a better cycle time and cycle time variance performance. In Figure 7(b), the calibration intervals are 10, 12, 24, 48 and 168 hours and the calibration effect is not as evident as in Figure 7(a), even worse for 48 and 168 hours cases. Table 1 shows four performance measures of the matrix table without calibration and with calibration during 2, 4, 6, 8, 10, 12, 24, 48, 168 hours interval. It is obvious that the performances are improved when the calibration interval is small such as from 2 hours to 24 hours. When the calibration interval is large like 48 hours and 168 hours, the performances are even worse than the one without calibration. The reason is the earlier to monitor WIP abnormity, the more accurate to capture the WIP imbalance phenomenon. If the interval is large, we may miss the opportunity to calibrate when WIP imbalance phenomenon.

## Zhou and Rose

ance occurs. Then the small WIP imbalance can develop into serious problem over time. It is a huge challenge to correct for the enlarged WIP imbalance. It tells us that the WIP abnormity phenomenon has to be monitored any time and calibrated as soon as possible.

(a) Every 2, 4, 6, 8 hours

(b) Every 10, 12, 24, 48, 168 hours

Figure 7: WIP evolution curve of priority matrix table applied with WIP calibration approach every 2, 4, 6, 8, 10, 12, 24, 48, 168 hours.

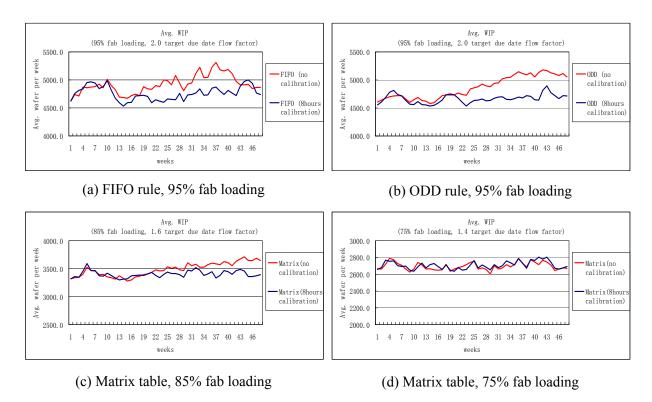

Figure 8 also shows us the proposed WIP monitor and calibration approach can be adapted to other cases that different dispatching rules like FIFO and ODD are applied as default rules. The robustness of proposed WIP calibration approach is tested in the following way. First, the default dispatching rule is changed from Matrix table to FIFO and ODD. Then the fab loading is changed from 95% to 85% and 75% cases. The simulation results indicate that the proposed WIP calibration approach succeeds in correcting for WIP imbalance as long as it occurs.

Table 1: Four performance measures of priority matrix table with and without WIP calibration

| Matrix         | Avg. Cycle Time (days) | Cycle Time Variance (days^2) | Pct. Tardy Lots (%) | Avg. Tardiness for<br>Tardy Lots (days) |

|----------------|------------------------|------------------------------|---------------------|-----------------------------------------|

| No calibration | 27.8                   | 0.64                         | 35.3                | 0.74                                    |

| 2 hours        | 27.6                   | 0.62                         | 21.2                | 0.59                                    |

| 4 hours        | 27.2                   | 0.65                         | 15.3                | 0.61                                    |

| 6 hours        | 27.4                   | 0.62                         | 19.4                | 0.64                                    |

| 8 hours        | 26.7                   | 0.81                         | 7.3                 | 0.95                                    |

| 10 hours       | 27.6                   | 0.62                         | 27.9                | 0.62                                    |

| 12 hours       | 27.6                   | 0.60                         | 23.9                | 0.60                                    |

| 24 hours       | 27.4                   | 0.61                         | 20.5                | 0.56                                    |

| 48 hours       | 28.3                   | 0.80                         | 49.5                | 0.73                                    |

| 1 week         | 27.8                   | 0.61                         | 39.5                | 0.66                                    |

### Zhou and Rose

Figure 8: WIP curve evolution of different rules with different fab loading, with calibration vs. without calibration

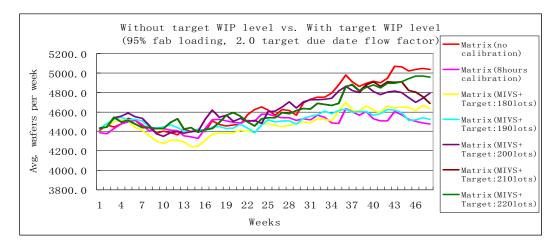

# 3.3 WIP Calibration with vs. without Target WIP Level

The previous section demonstrates that the proposed WIP calibration approach is able to drag the WIP curve back to the right track without applying target WIP level in case WIP imbalance occurs. However, we are curious about whether the performance of proposed WIP calibration approach is as good as the one applying target WIP level. Therefore, another WIP correction action with MIVS rule depicted in Figure 4(b) is employed. We only pick up the WIP curve of matrix table with proposed calibration approach of 8 hours interval as bench mark. In Figure 9, when the target WIP levels of fab are 180 and 190 lots, the WIP curves of MIVS correction are as flat as the case of proposed WIP calibration approach. As the fab target WIP level raises, because the frequency of WIP monitor and correction decreases, some WIP imbalance phenomenon can not be captured and calibrated, which leads to a similar climbing WIP curve as the one without any correction. The detailed performance measures are showed in Table 2. The cycle time difference is almost 1 day if the fab target WIP level rises from 180 to 200 lots. It tells us again the target WIP level correction oriented approach is difficult to apply since a missed target WIP level could result in huge performance degradation.

The proposed WIP calibration approach is inspired by MIVS. These are the two reasons why MIVS is successful. (1) When operation i has high WIP and its next downstream operation i+1 has low WIP, MIVS gives higher priority to operation i in order to avoid the starvation at operation i+1; (2) MIVS uses target WIP level to minimize the deviation between the actual WIP and target WIP level. For our proposed WIP calibration approach, firstly our approach has the mechanism to push WIP from high WIP upstream to low WIP downstream. On one hand, it can ensure the high WIP block has output for the low WIP block. On the other hand, it can make sure WIP balance inside the block. Secondly, similar to MIVS but our approach uses historical average WIP level to replace target WIP level. This historical average WIP level plays the role for target WIP level. In case the WIP imbalance occurs, this historical average WIP level

### Zhou and Rose

represents the average WIP during the last 'X' hours, and during the last 'X' hours the WIP is in a balanced state. We can see that when the WIP becomes imbalanced state from balanced state, the historical average WIP during the last 'X' hours becomes the theoretical target WIP level which we want to achieve. We want to minimize the deviation between the actual WIP and the historical average WIP, to make sure the WIP turn into balanced state again. Different from the target WIP level the historical average WIP level changes all the time and depends on the 'X' hours. In addition, with the assistance of ODD rule we know exactly which lots are needed to be pushed to downstream to balance the WIP.

Figure 9: WIP curve evolution of matrix table applied calibration with vs. without target WIP level

Table 2: Four performance measures comparison of matrix table applied calibration with vs. without target WIP level

| Matrix              | Avg. Cycle Time (days) | Cycle Time Variance (days^2) | Pct. Tardy Lots (%) | Avg. Tardiness<br>for Tardy Lots<br>(days) |

|---------------------|------------------------|------------------------------|---------------------|--------------------------------------------|

| No calibration      | 27.8                   | 0.64                         | 35.3                | 0.74                                       |

| 8 hours calibration | 26.7                   | 0.81                         | 7.3                 | 0.95                                       |

| MIVS +<br>180Lots   | 26.8                   | 0.49                         | 8.0                 | 0.18                                       |

| MIVS +<br>190Lots   | 27.0                   | 0.50                         | 5.2                 | 0.25                                       |

| MIVS +<br>200Lots   | 27.6                   | 0.66                         | 30.9                | 0.72                                       |

| MIVS +<br>210Lots   | 27.5                   | 0.67                         | 27.0                | 0.61                                       |

| MIVS +<br>220Lots   | 27.6                   | 0.63                         | 30.5                | 0.65                                       |

### 4 SUMMARY

In this paper, we proposed a priority matrix table which prioritizes lots according to the information of work-center's workload and lot's due date in order to keep the lots going through the fab at the right pace to achieve WIP balance. Besides that, a WIP monitor and calibration approach differentiating traditional WIP correction approach was also proposed. The major contribution of this study lies in the WIP calibration approach is able to achieve WIP correction without the assistance of target WIP level. The simulation results implies that the proposed WIP calibration approach is robust since it can be employed to correct for WIP imbalance no matter which default dispatching rule or fab loading is used. The performance is still as good as the one like MIVS which applies target WIP level. It gives us hints we may abandon target WIP level in the future study since it is extremely difficult to determine and apply an appropriate target WIP level to the operations or work-centers. For the future research, more datasets have to be tested by the proposed WIP calibration approach to validate its accuracy and robustness.

#### REFERENCES

- Baker, K. R., and J. W. M. Bertrand. 1981. "A Comparison of Due-Date Selection Rules." *AIIE Transactions* 13:123-131.

- Dabbas, R.M. and J. Fowler. 2003. "A New Scheduling Approach Using Combined Dispatching Criteria in Wafer Fab." IEEE TRANSACTIONS ON SEMICONDUCTOR MANUFACTURING 16:501-510.

- Fowler, J., and J. Robinson. 1995. "Measurement and Improvement of Manufacturing Capacities (MIMAC): Final report." Technical Report 95062861A-TR, SEMATECH, Austin, TX.

- Kuo, C., C. Liu and C. Chi. 2008. "Standard Wip Determination and Wip Balance Control with Time Constraints in Semiconductor Wafer Fabrication." Journal of Quality 15:409-423.

- Leachman, R.C., J. Kang, and V. Lin. 2002. "SLIM: Short Cycle Time and Low Inventory in Manufacturing at Samsung Electronics." INTERFACES 32:61-77.

- Li, S., T. Tang, and D. W. Collins. 1996. "Minimum inventory variability schedule with applications in semiconductor fabrication". IEEE TRANSACTIONS ON SEMICONDUCTOR MANUFACTURING 9:1–5.

- Zhou, Z., and O. Rose. 2010. "A Pull/Push Concept for Tool Group Workload Balance in a Wafer Fab." In *Proceedings of the 2010 Winter Simulation Conference*, edited by B. Johansson, S. Jain, J. Montoya-Torres, J. Hugan, and E. Yücesan, 2516-2512. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

## **AUTHOR BIOGRAPHIES**

**ZHUGEN ZHOU** is a PhD student at University of the Federal Armed Forces Munich, Germany. He is a member of the scientific staff of Prof. Dr. Oliver Rose at the Chair of Modeling and Simulation. He received his M.S. degree in Computational Engineering from Dresden University of Technology. His research interests include dispatching concepts for complex production facilities and work-center modeling for wafer fab. His email address is <a href="mailto:zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhugen.zhu

**OLIVER ROSE** holds the Chair for Modeling and Simulation at the Department of Computer Science, University of the Federal Armed Forces Munich, Germany. He received an M.S. degree in applied mathematics and a Ph.D. degree in computer science from Würzburg University, Germany. His research focuses on the operational modeling, analysis and material flow control of complex manufacturing facilities, in particular, semiconductor factories. He is a member of IEEE, INFORMS Simulation Society, ASIM, and GI, and General Chair of WSC 2012.