#### 300MM WAFER FABRICATION LINE SIMULATION MODEL

Sameer T. Shikalgar David Fronckowiak

IBM Microelectronics Division East Fishkill, NY 12533, U.S.A.

#### ABSTRACT

The importance of semiconductor wafer fabrication has been increasing steadily over the past decade. Wafer fabrication is the most technologically complex and capital intensive phase in semiconductor manufacturing. It involves the processing of wafers of silicon in order to build up layers and patterns of metal and wafer material. Many operations have to be performed in a clean room environment to prevent particulate contamination of wafers. Also, since the machines on which the wafers are processed are expensive, service contention is an important concern. All these factors underline the importance of seeking policies to design and operate them efficiently. We describe a simulation model of a planned 300mm wafer fabrication line that we are using to make strategic decisions related to the factory.

### **1 INTRODUCTION**

A development level model of a 300mm wafer fabrication line was constructed to make design decisions for 75 wafer starts per day (WSD) (Campbell and Laitinen, 1997; Campbell and Norman, 1998; Campbell and Norman, 1999). This model contains approximately 100 tools. This development model was used as the basis for the construction of a model for a 200mm line for Dominion Semiconductor (Norman and Barksdale, 1999). This model has been expanded to represent a production environment capable of sustaining 400 to 800 WSD (approximately 300 to 600 tools). This model is being used to make further design decisions for the manufacturing line.

300mm wafers (approximately 12 inches in diameter) are going to replace 200mm wafers that are currently in wide use in the semiconductor industry. The larger wafer size requires an entirely new tool set. The 300mm wafers are transported using wafer carriers. Due to the increased size of the wafers, the carriers are heavier than 200mm wafer carriers and hence an automated material handling system is used to deliver wafers to the tools.

Edward A. MacNair

IBM T.J. Watson Research Center Yorktown Heights, NY 10598, U.S.A.

The paper includes sections discussing the details of the model including the tool processing, the automated material handling system, and the experiments being conducted. We are investigating several operations management policies designed to optimize the working of the factory. Results of experiments conducted with the model are discussed.

### 2 MODEL DETAILS

The model was built with simulation tools from Brooks Automation, including AutoSched<sup>TM</sup> AP and AutoMod<sup>TM</sup>. The model consists of two distinct parts, the tool processing system, which is modeled using AutoSched<sup>TM</sup> AP and the material handling system that delivers the wafers to the tools for processing, which is modeled using AutoMod<sup>TM</sup>. The two models communicate with each other using MCM (Model Communications Module), which is also a product of Brooks Automation. For each instance of a move that is required from a tool to another tool or from a tool to a storage location, a move request is sent from AutoSched<sup>TM</sup> AP to AutoMod<sup>™</sup> using the MCM. AutoMod<sup>™</sup> uses the designed material handling system to move the lot to the specified location. When the move is completed, a move complete message is sent from AutoMod<sup>™</sup> to Auto-Sched<sup>TM</sup> AP. AutoSched<sup>TM</sup> AP then continues with the processing of the lot.

### 2.1 Tool Processing

The tool processing part of the model consists mainly of spreadsheets describing the tools and the routing steps the wafers follow through the tools during the wafer fabrication process. Each tool is located in a bay and has a tool group name, a scheduling rule, load and unload times, and primary and alternate stockers. Also, each tool has a number of load ports, which are used to hold the lots for processing at the tool. There are four types of tools: wafer-by-wafer, batch, chamber and pipeline. Wafer-by-wafer tools use fixed and variable times to model the processing of a lot. The fixed time is taken irrespective of the number of wafers in a lot and the variable time is added for each wafer.

Batch tools form a group of lots that can be processed simultaneously. The maximum batch size is defined for each tool and a batch criterion is used to batch lots that arrive at a tool.

Chamber tools have definitions for chambers and robots. Chamber tools improve the capability of the model to plan each process on the tool and consequently determine the number of chambers for each type of chamber. For each chamber tool, the different types of chambers on the tool and a robot are defined. When a lot arrives at a chamber tool in a route, it is transferred to a chamber tool subroute where the sequence of processing within the chamber tool is specified. After completing processing on a chamber tool the lot is transferred back to its main route.

Pipeline tools are used to model wetbenches. The lots are batched together and processed in sinks. Since the tools have more than one sink, multiple batches can be processed at the same time.

Each step in the wafer routing contains the tool group name, tool type, processing time parameters and setup information. Some steps have alternate tool types that can be used if all of the primary tools are busy. Also tools within a tool group can be dedicated to certain operations using a tool specification at the operation. Equipment dedication can reduce setups and increase throughput capability. Similar equipment capable of performing several processes is sometimes divided into two or more tool groups. Each tool group is then qualified to execute a subset of the processes or recipes for which it is capable of performing. Such dedication of tools to recipes is employed partly to reduce or eliminate long setups required when switching recipes.

Reticles are modeled as generic resources and are requested at every photolithography step in the route.

Sampling is done on metrology tools. If a lot is selected for processing at a metrology tool only a subset of the wafers are processed. This is determined using a PercentWafersProcessed field in the route.

Rework percentages are defined for metrology steps following a photolithography step. If a lot is selected for rework it is transferred to a rework route. After completing processing at a rework route the lot is joined to the main route at the photolithography step immediately preceding the metrology step.

Each tool has preventive maintenance and down time distributions associated with it. These are used to model planned and unplanned maintenance on the tools. Down events causes preemption of the lots on tools. If a lot is preempted at a tool the lot will wait at the tool and continue processing when the tool is released from the down event.

#### 2.2 Automated Material Handling Systems (AMHS)

The interbay/intrabay AMHS represents vehicles on an overhead centralized monorail for interbay movement and an overhead hoist transporter for intrabay movement. The intrabay and interbay systems interface through stockers at the end of each bay. The stockers are used for lot storage and also serve as a bridge between the interbay and the intrabay systems. Two different types of vehicles are used, one each for the interbay and the intrabay. The interbay system links all the bays together. Hence any move from one bay to another would involve the interbay system. The interbay vehicle retrieves and delivers lots only to stockers and can carry two lots at a time.

The intrabay vehicles can only move lots within a single bay. The vehicles can carry only one lot at a time and move lots to the load ports of the tools.

Stockers are modeled as Automated Storage/Retrieval Systems (ASRS). Each stocker has a robot, which moves lots to and from the interbay and intrabay systems.

The parameters for the AMHS are stored in a specifications file in AutoSched<sup>TM</sup> AP. The parameters include velocities and accelerations for the vehicles and stocker robots, pickup and setdown times, and down times for the vehicles.

The material handling system can be operated in one of two modes: push or pull. In the push mode, lots are pushed to the next tool if there is at least one lot port available. In the pull mode, a lot is pulled to a tool when the tool is ready to process it.

### 2.3 Orders

Orders of lots are released into the line. There are three types of lots in the model: normal, priority, and qualification lots. Each lot has a time between release based on the specified wafer starts per day, the lot size, and the percent of each product in the product mix. The product mix is distributed over a large variety of products with each product having approximately 400 - 600 process steps.

### 2.4 Qualification Lots

Tools in the factory need to be qualified on a regular basis. For this, qualification lots are processed on the tool to ensure that the tool is running within specifications. The frequency and the type of qualification vary according to tool type. Qualification lots decrease the availability of the tools due to non-product processing. This increases the cycle time on product lots. Qualification lots are released to the factory similar to regular products, however the lots are only used to preempt the processing of the tool. The cycle time of the qualification lots is not calculated as part of the overall factory cycle time.

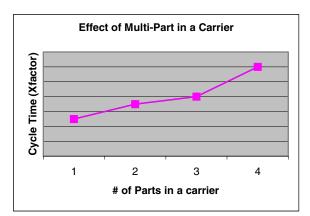

### 2.5 Multi-Part Lots

Due to the increased size of 300mm wafers, more chips are produced on a single wafer. Having a large number of wafer carriers in the factory would increase the load on the Automated Material Handling System. Hence to maximize lot processing capability and wafer output, multiple lots per carrier may be required. Hence, multi-part lots are planned to reduce transportation time. For multi-part carriers, all the wafers in a carrier do not belong to the same part and do not undergo identical processing at the tools. However the different parts follows similar routes to minimize the cycle time of the lot. Various experiments were conducted using different numbers of parts in a carrier.

## **3** DATA VALIDATION

All the data used for the simulation model are from process and vendor estimates for the tools. As the factory is being installed and the tools are ready for processing, the data from the simulation is being validated with the actual processing times of the tools.

### 4 EXPERIMENTS

To make the correct strategic decisions for a 300mm wafer fabrication line we must understand the effect of various operations management policies, product and process diversity, demand fluctuations, and factory scale.

Operations management alternatives include different lot sizes, different lot priorities, lot scheduling and multiparts in a carrier analysis.

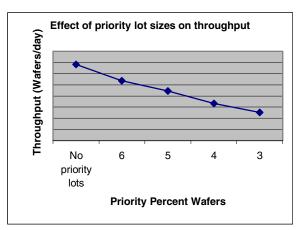

Experiments were conducted with one product per lot with 24, 18, and 12 wafers per lot. The impact of lot sizes on the transportation time was also studied. Other experiments studied the feasibility of increasing the percentage of priority wafers in the factory.

## 5 DISCUSSION OF RESULTS

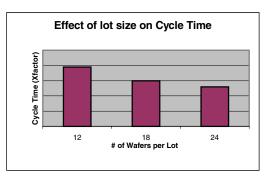

The first experiment was a comparison of different lot sizes. As shown in Figure 1, runs were made with 24, 18, and 12 wafers per lot.

Figure 1: Effect of Lot Size on Cycle Time

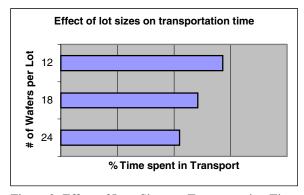

The impact of reducing the number of wafers in a lot resulted a significant increase in transportation time, as shown in Figure 2.

Figure 2: Effect of Lots Sizes on Transportation Time

The reduction in throughput by the increasing number of priority wafers is shown in Figure 3.

Figure 3: Effect of Priority Lot Sizes on Throughput

Experiments were also conducted with multiple parts in a single carrier. Experiments were carried out with 2, 3 and 4 parts in a carrier, as shown in Figure 4.

Figure 4: Effect of Multi-Parts in a Carrier

### 6 RUN LENGTHS

Experiments were conducted to determine the length of the warmup period and the total run length. It was found that when the percent idle time for the bottleneck tool is above 10%, a warmup period of 40 days and a total run length of 120 days is sufficient. When the percent idle time for the bottleneck tool is between 5% and 10%, a warmup period of 60 days and a total run length of 160 days is sufficient. When the percent idle time for the bottleneck tool is less than 5%, a much longer run is necessary.

The average time taken to complete a run using Auto-Sched<sup>TM</sup> AP, AutoMod<sup>TM</sup> and MCM is approximately 24 hours. This is not feasible if a number of runs are required in a short period of time. An alternative has been developed by generating a From/To matrix from the AutoMod<sup>TM</sup> model. The From/To matrix consists of the average travel time, during the simulation, from one tool to another, for all moves. The AutoSched<sup>TM</sup> AP model can then run stand-alone without AutoMod<sup>TM</sup> or MCM, using the From/To matrix every time a move is needed. This reduces the average run time to approximately 3-4 hours.

## 7 PROPOSED RESEARCH

Lot release and lot dispatching rules have a significant impact on cycle time for a semiconductor manufacturing facility. Presently, experiments are being conducted to develop a policy to release and dispatch lots in the factory. The simulation model provides a valuable tool to analyze the working of different rules.

Batch sizes and the time waiting to form a batch at a batch machine greatly influence factory performance. Batch machines have a time period called wait no longer than time (WNLTTM), which is used as the time period to form a batch. Experiments are being conducted with different algorithms and WNLTTM's to minimize cycle time of the factory.

# 8 SUMMARY

The model of the 300mm wafer fabrication line discussed in this paper contains a very realistic representation of a future factory. We are using this model to make strategic decisions related to the design and operation of the semiconductor factory.

# ACKNOWLEDGMENTS

We wish to acknowledge the discussions with and the support from our colleagues including Phil Campbell, Tom Walsh, and Sarah Hood.

### REFERENCES

- Campbell, P., and G. Laitinen. 1997. Overhead Intrabay Automation and Microstocking – a virtual fab case study. In Proceedings of the IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop, 368-372. Cambridge, MA.

- Campbell, P., and M. Norman. 1998. Microstocking and Fab Throughput. In *Proceedings of the AutoSimulations '98 Symposium*, 101-106. Bountiful, UT.

- Campbell, P., and M. Norman. 1999. Simulation Used To Model And Test Improvements In 300 Mm Fab Throughput. Available online via <a href="http://www.semi">http://www.semi</a> condutoronline.com>.

- Norman, M., and J. Barksdale. 1999. Integrated Manufacturing and Material Handling Simulation Modeling. In *Proceedings of the SIMULATION Solutions '99 Conference*. Mesa, AZ.

## **AUTHOR BIOGRAPHIES**

SAMEER T. SHIKALGAR is an Industrial Engineer in IBM's Microelectronics Division. He has worked in the areas of modeling and analysis of semiconductor processes. He holds a M.S. in Industrial Engineering from Virginia Polytechnic and State University and a B.E. in Production Engineering from Mumbai University, India. His email address is <sshik@us.ibm.com>.

DAVID FRONCKOWIAK is the manager of the 300mm Industrial Engineering Department in IBM's Microelectronics Division. He has worked in the modeling and simulation of semiconductor processes with emphasis on fab productivity improvement for 10 years. He holds a M.S. in Industrial Engineering from The University of Arizona and an MBA from Marist College. His email address is <fronckow@us.ibm.com>.

EDWARD A. MACNAIR specializes in modeling contention systems in IBM Research's Mathematical Sciences Department. He has more than 35 years of experience at IBM and has worked in the areas of modeling systems and model tool development. Mr. MacNair holds a M.S. in Operations Research from New York University and a B.A. in Mathematics from Hofstra University. His email address is <emacnair@us.ibm.com>.