# A MATHEMATICAL MODEL FOR ESTIMATING DEFECT INSPECTION CAPACITY WITH A DYNAMIC CONTROL STRATEGY

Gloria Luz Rodriguez-Verjan<sup>1,2</sup> Stéphane Dauzère-Pérès <sup>1</sup> Jacques Pinaton<sup>2</sup>

<sup>1</sup>Department of Manufacturing Sciences and Logistics Ecole Nationale des Mines de Saint-Etienne - CMP F-13541 Gardanne, FRANCE <sup>2</sup>STMicroelectronics Rousset F-13106 Rousset, FRANCE

### **ABSTRACT**

In this paper, we introduce a mathematical model for estimating the use of defect inspection capacity. Until recently, the selection of lots to be inspected was only done at the beginning of the manufacturing process. With the introduction of dynamic controls on production tools, the selection of lots to be inspected is done according to the production state. Our problem focuses on the Wafer at Risk (W@R) on process tools. The W@R is the number of processed wafers between two control operations. The W@R depends on several factors such as the availability of measurable products, control limits, defect inspection capacity and defect inspection control plans of products. Our model aims at calculating the defect inspection capacity required for given values of the listed factors. Experimental results on actual factory data are presented and discussed.

# 1 INTRODUCTION

With the increasing demand for more powerful and faster devices, semiconductor manufacturing processes are constantly becoming more complex. The high level of integration, the molecular scope of operations and the re-entrant flow of the process make Integrated Circuits more complex and expensive to produce. Therefore, regular inspections are introduced to ensure high quality of finished products (May and Spanos 2006). However, metrology and inspection capacity is costly and limited. Moreover, inspections have a direct impact on cycle times (Tirkel et al. 2009). This is why several sampling strategies have been proposed to find a trade-off between the number of inspections and the yield of products. According to the selection rules, the existing strategies can be classified as Static, Adaptive and Dynamic Sampling. A complete literature review concerning the Sampling techniques can be found in (Nduhura Munga et al. 2012). With the Static Sampling and Adaptive Sampling, lots are selected at the beginning of the manufacturing process, the main difference is that with the Static strategy the sampling rate is fixed and with the Adaptive Strategy the sampling rate is variable according to the production state. With the Dynamic Sampling no rule is defined at the beginning of the manufacturing process, the decision is taken in front of the inspection operation and lots are selected in real time according to the workload of inspection tools and the information that can be gained when the lot is measured. Allocation of inspection resources is one of the main concerns when defining the Sampling Strategy.

Among the studies that focus on the inspection allocation when a static sampling strategy is used, we can find Nurani et al. (1994). They propose a model to optimize the number of lots to inspect, the number of wafers within a lot and the number of dies per wafer according to economics of inspections in the full production phase. Gudmundsson (2005) propose two models to allocate inspection capacity, one model is based on the rump up phase and the other is based on the full production phase. A genetic algorithm is developed in order to resolve the model for the full production phase. Experiments to compare different investment decisions are performed. When the sampling rate is variable, the complexity to determine the allocation

capacity increases. Song-bor et al. (2003) propose an adaptive sampling strategy based on the workload of inspection tools. The system is composed of two main functions, when the utilization rate of inspection tools is too high, a function that allows WIP Skipping is activated. When the utilization rate drops too low, then a function that forces WIP executing defect inspection is activated. Nduhura Munga et al. (2011) present an adaptive sampling strategy based on the real time computation of Wafer at Risk. Concerning the Development of Dynamic Sampling strategies first works date from 2005 with the publication of Purdy et al. (2005). They propose a method to manage the waiting queue in metrology where lots with more recent data are more suitable to being measured. In consequence, lots that provide redundant information could be removed from the queue. Hyung Joo Lee (2008) propose a model that combines the cost of sampling with the performance of control in terms of yield and cycle time. Dauzère-Pérès et al. (2010) propose a Dynamic Sampling method to choose the best set of lots to measure according to a Global Score (GSI). With this strategy, measures are optimized since the selection of redundant lots (i.e. lots with the same information) can be reduced.

Since the development of dynamic sampling is recent in literature, few works can be found that address the problem of inspection allocation capacity under a dynamic sampling strategy. In this paper, we present a novel approach to calculate the defect inspection capacity requirements when the dynamic sampling strategy presented in Dauzère-Pérès et al. (2010) is used. We focus on micro defect inspections where the flaws produced by particles are detected. The risk considered in this work is evaluated in terms of number of wafers processed on a tool since the last defect inspection performed (known as Wafer at Risk, W@R). In general, each time a lot is performed by a process tool, the W@R is incremented by the number of wafers of the lot. When a lot is controlled in a defect inspection operation, the W@R of the tools where the lot was processed can be reduced.

The structure of the paper is as follows. The problem is first defined in Section 2. Section 3 presents the mathematical model, and Section 4 is devoted to the analysis of some numerical experiments performed on real data. Finally, conclusions and perspectives are provided in Section 5.

### 2 PROBLEM DESCRIPTION

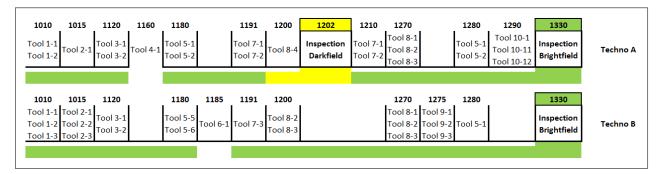

The route of a product is the list of operations that have to be performed to obtain the final IC. The route depends on the specifications of the technology to produce (e.g., type of device). The defect inspection control plan of a technology is the list of inspection operations that have to be performed during the manufacturing route. The control plan includes the position and the coverage of inspection operations. Integrated circuits are produced on silicon wafers that travel in lots, usually of 25 wafers. Figure 1 shows a small portion of the route for products of a technology "A" and the same portion of another route for products of another technology "B". In this figure, all lots of Technology "A" must go though process operations 1010 to 1200 and through process operations 1210 to 1290. Only some lots will be controlled on the inspection operations 1200 and 1330. The selection of lots that will be inspected is done according to a sampling strategy. The coverage block refers to the process operations that can be controlled with an inspection operation. In our example for Technology "A", the inspection operation 1202 covers the process operation 1200, and the inspection operation 1330 covers all the process operations except 1160 and 1200. The allocation and coverage of inspection operations depend upon the product and the detection capability of inspection tools. When a lot starts an inspection operation, the process tools that are covered are the ones on which the lot was processed. Traditionally, inspection operations are placed in the control plan between critical operations for the product (May and Spanos 2006). But, with the introduction of dynamic sampling strategies and the W@R on tools, new factors have to be taken into account in the design of defectivity control plans. As exposed in Rodriguez-Verjan et al. (2011), having more inspections in the control plan does not always reduce the overall W@R. Hence, the positions of control operations and how they cover process operations have a direct impact on the W@R reduction.

The qualification refers to a certain type of setup that is performed on the tool, and it assures the right conditions for the process (e.g., right temperature, metal composition, gas pressure). As discussed in

Figure 1: Product Route and Defectivity Control Plan Representation.

Johnzén et al. (2011), an efficient qualification management of process tools is necessary to improve the performance in work areas and the entire factory. In Figure 1, the products of both technologies have some common process operations, but the qualifications of process tools are different. For example, the product of Technology "A" must be performed on tool Tool 2-1 in process operation 1015 whereas, for the product of Technology "B", the same process operation 1015 can be performed on three process tools. Concerning the qualification of inspection tools, in our example, the inspection operation 1202 must be performed with a Darkfield tool and the inspection operation 1330 can be performed with a Brightfield tool. Since the qualification of tools defines which products can be processed or controlled on the different operations of its route, this is an important information to consider because it is directly linked to the resulting Wafer at Risk on the process tool.

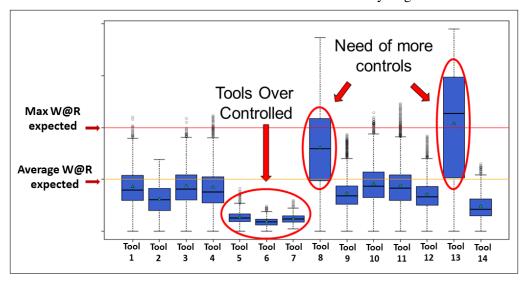

As exposed in Nduhura Munga et al. (2011), when lots to be inspected are selected at the beginning of their manufacturing process, an optimal control of process tools in terms of W@R cannot be guaranteed. This is due to the inherent characteristics of the manufacturing process, such as tool recipe qualifications, re-entrant flows, position and coverage of inspection operations, etc. Consequences are several cases of over-control and lack of control on process tools. Figure 2 illustrates these phenomena with actual historical data for tools in the same area. It can be observed that the W@R of some tools always remains very small while both the mean and the variance of the W@R of other tools is very large.

Figure 2: W@R on tools in the same area.

In order to reduce these cases of over-control and lack of control on tools, a dynamic sampling strategy has been implemented. Two key parameters are necessary to master the Wafer at Risk (W@R) on tools: The Warning Limit (WL) and the Inhibit Limit (IL). The Inhibit limit is the maximum value of acceptable W@R for process tools. If the W@R reaches the Inhibit limit, the process tool is automatically stopped and a special control has to be performed. The Warning Limit refers to the limit after which the situation is considered critical and a lot has to be inspected. Thus, the Warning Limit gives the required frequency of measures for a process tool. Nduhura Munga et al. (2011) propose an Integer Linear Program that determines the Warning Limits and Inhibit Limits for a given inspection capacity.

The problem presented in this paper consists of planning the inspection capacity when the W@R on tools is considered and a dynamic sampling strategy is used to sample lots. The presented model aims at answering how much inspection capacity is needed if some of the following factors change:

- W@R Limits (i.e. Warning Limit and Inhibit Limit) on process tools,

- Qualifications of process tools,

- Qualifications of inspection tools,

- Mixes and volumes of products,

- Positions and coverage of inspection operations.

The W@R limits define the frequency of lots that need to be inspected for process tools, thus with a continuous reduction of W@R limits, the frequency of controls has to increase. As mentioned before, the qualification of process tools determines the products that can be processed on these tools. Thus, the mixes and volumes of products directly influence the W@R of process tools. In addition, the control plan of a product defines the position and coverage of inspection operations. Consequently, modifying the product mix can lead to situations where W@R limits cannot be guaranteed and where the workload on inspection tools is not balanced.

# A MATHEMATICAL MODEL FOR DEFECTIVITY CAPACITY ALLOCATION

This section describes the Linear Program (LP) proposed to calculate the requirements in terms of number of measures to ensure given levels of W@R on Tools. The parameters are:

- $V^i$ : Production Volume of Product i,

- $WL_t$ : Warning Limit of process tool t,

- *nbT*: Number of process tools,

- *nbI*: Number of products,

- *nbC*: Number of control operations,

- *nbK*: Number of inspection tool types,

- $e_{c,p}^i$ : is equal to 1 if the inspection operation c of product i covers the tools of process operation p and 0 otherwise,

- $b_{ck}^i$ : is equal to 1 if the control operation c of product i is qualified for inspection tool type k and 0 otherwise,

- $h_p^i$ : is equal to 1 if product i is processed on process operation p and 0 otherwise,

- $hh_{p,t}^{i}$ : is equal to 1 if process tool t is qualified to process product i in process operation p and 0

- $E\_CAPA_k$ : Capacity available for inspection tool type k.

# The decision variables are:

- $XV_{p,t}^i$ : Production volume of product i processed on tool t in process operation p,  $YC_{c,p,t}^i$ : Number of controls of product i in control operation c that covers process tool t of process operation p,

- $ZCC_c^i$ : Total Number of controls performed in control operation c of product i,

- A\_CAPA<sub>k</sub>: Capacity needed for inspection tool type k.

The objective is to minimize the additional defect inspection capacity required to guarantee the Warning Limits on process tools.

$$\min \sum_{k=1}^{nbK} A_{-}CAPA_{k}$$

s.t.

$$\sum_{t=1}^{nbT} X V_{p,t}^{i} \cdot h h_{p,t}^{i} = h_{p}^{i} \cdot V^{i} \qquad \forall t \in \{1,...,nbP\}, \forall i \in \{1,...,nbI\} \qquad (1)$$

$$C_{c,p,t}^{i} \geq \frac{\sum_{i=1}^{nbI} \sum_{p=1}^{nbP} X V_{p,t}^{i}}{\sum_{p=1}^{nbP} X V_{p,t}^{i}} \qquad \forall t \in \{1,...,nbT\} \qquad (2)$$

$$\sum_{i=1}^{nbI} \sum_{c=1}^{nbC} \sum_{p=1}^{nbP} YC_{c,p,t}^{i} \ge \frac{\sum_{i=1}^{nbI} \sum_{p=1}^{nbP} XV_{p,t}^{i}}{WL_{t}} \qquad \forall t \in \{1,...,nbT\} \qquad (2)$$

$$YC_{c,p,t}^{i} \le XV_{p,t}^{i} \quad \forall t \in \{1,...,nbT\}, \forall c \in \{1,...,nbC\}, \forall i \in \{1,...,nbI\}$$

$$\forall p \in \{1, ..., nbP\} \text{ s.t. } hh_{n,t}^i = 1 \text{ and } e_{c,p}^i = 1$$

(3)

$$ZCC_c^i \le \sum_{t=1}^{nbT} YC_{c,p,t}^i \cdot hh_{p,t}^i$$

$\forall p \in \{1,...,nbP\} \text{ s.t. } e_{c,p}^i = 1$  (4)

$$A\_CAPA_k + E\_CAPA_k \ge \sum_{c=1}^{nbC} \sum_{i=1}^{nbI} ZCC_c^i \cdot b_{c,k}^i$$

$\forall k \in \{1, ..., nbK\}$  (5)

$$\forall V_{p,t}^i \ge 0 \qquad \forall p \in \{1,...,nbP\}, \forall i \in \{1,...,nbI\}$$

$$YC_{c,n,t}^{i} \ge 0$$

$\forall p \in \{1,...,nbP\}, \forall i \in \{1,...,nbI\}$

$$\forall t \in \{1, ..., nbT\}, \forall t \in \{1, ..., nbC\}$$

$$\forall t \in \{1, ..., nbT\}, \forall c \in \{1, ..., nbC\}$$

$$(7)$$

$$ZCC_c^i > 0 \qquad \forall c \in \{1, ..., nbC\}, \forall i \in \{1, ..., nbI\}$$

(8)

$$A\_CAPA_k \ge 0 \qquad \forall k \in \{1, ..., nbK\} \qquad (9)$$

$$XV_{p,t}^i \in \mathbb{R}^+$$

$\forall i \in \{1,...,nbI\}, \forall p \in \{1,...,nbP\}$

$$\forall t \in \{1, ..., nbT\} \quad (10)$$

$\forall t \in \{1,...,nbT\}$

(6)

$$YC_{c,p,t}^{i} \in \mathbb{R}^{+} \qquad \forall c \in \{1,...,nbC\}, \forall p \in \{1,...,nbP\}$$

$$\forall t \in \{1, ..., nbT\}, \forall t \in \{1, ..., nbI\} \quad (11)$$

$$ZCC_c^i \in \mathbb{R}^+$$

$\forall i \in \{1, ..., nbI\}, \forall c \in \{1, ..., nbC\}$  (12)

Constraint (1) defines how the volume of product i is processed among process tools t that are qualified for process operation p. Constraint (2) expresses the requirements in number of controls for process tool t. This number is calculated as the total volume processed on tool t divided by its Warning Limit. Constraint (3) ensures that the number of controls assigned to process tool t cannot be larger than the total volume produced on tool t. Constraint (4) determines the coverage of controls. It states how the total number of controls performed in control operation t0 are assigned to process tools that are covered. Constraint (5) balances the total number of controls assigned to each inspection tool type. Constraints (6) to (9) assure that the value assigned to the decision variables is positive. Finally, constraints (10) to (12) define the type

of decision variables. Since our objective is to estimate the required measurement capacity in a reasonable CPU time, we considered real variables instead of integer variables.

### 4 EXPERIMENTAL STUDY AND RESULTS

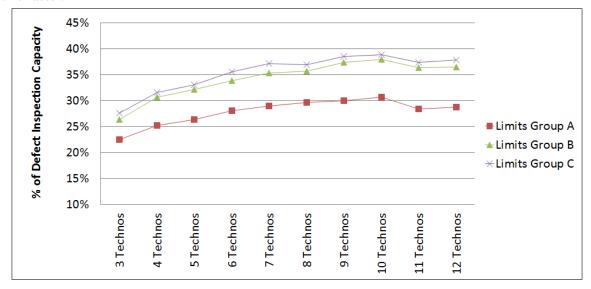

We ran the proposed LP model on real data from STMicroelectronics to calculate the defect inspection capacity requirements. We considered more than 350 process tools, 1800 process operations, 170 control operations and 12 technologies. The model was developed in CPLEX 12.3 and experiments were run on a PC Intel Core i5 (2.40 GHz). In order to calculate the total defect capacity requirements, E\_CAPA was set to 0 for all inspection tool types. Figure 3 shows the impact in terms of inspection capacity when W@R limits are reduced. The x-axis represents the percentage of required defect capacity, the y-axis represents the number of technologies considered in each experiment. The limits in Group A correspond to the current W@R limits of process tools. The objective was to perform a campaign of limits reduction. Limits in group B correspond to the first set of reductions. Limits of group C correspond to the last set of reductions. The gaps between limits A and B are explained by the fact that the Warning limits for some tools were reduced by over 60%. The gaps between limits B and C correspond to an additional reduction of 30%. Let us focus on the results for 10 and 11 technologies. We can observe that there is a reduction on the capacity requirements even if the total volume of products have increased. This can be explained by the fact that the control plan is different according to the product. The new technology in group 11 has some controls for which the coverage is larger, and consequently the model selects control operations that cover more process tools, i.e. more tools are controlled by measuring one lot. Details on the design of control plans can be found in Rodriguez-Verjan et al. (2011). In the current version of our model, the delay time to get the results of measures has not been integrated. This is an important factor that can change the decisions concerning the selection of the inspection operations, and our current work is focusing on the integration of this factor.

Figure 3: W@R limit reduction vs. Defect inspection capacity.

Table 1 presents the results obtained with the current level of the W@R limits and different mixes and volumes of products. It shows the Total required capacity for a given set of W@R limits and a mix of products. Let us focus on Mix 1, in order to guarantee the W@R limits on process tools, it will be necessary to reserve 30,7% of the defect inspection capacity. This required capacity for Tool Type 1 (16,0%), Tool Type 2 (10,0%) and Tool Type 3 (4,7%). These results can help engineers from the Defectivity area to anticipate the qualification of inspection tools.

Let us focus on Mix 4 and Mix 7. It can be observed how the workload balance on the inspection tools changes, in particular the workload on the inspection tools of Type 1 decreases from 22.6% to 17.0% and the workload on the inspection tools of Type 2 increases from 16.7% to 19.0%. This is mainly due to the fact that the manufacturing route of each technology is different. Hence, the position, number and qualification of controls is also different as exposed in Section 2.

| Inspection Tools          | Mix 1 | Mix 2 | Mix 3 | Mix 4 | Mix 5 | Mix 6 | Mix 7 | Mix 8 |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                           |       |       | _     |       |       |       |       |       |

| Tool Type 1               | 16.0% | 15.8% | 12.4% | 22.6% | 14.0% | 19.9% | 17.0% | 17.4% |

| Tool Type 2               | 10.0% | 10.2% | 11.4% | 16.7% | 14.8% | 12.6% | 19.0% | 12.5% |

| Tool Type 3               | 4.7%  | 4.5%  | 8.8%  | 7.2%  | 7.4%  | 5.8%  | 10.4% | 7.0%  |

| Tool Type 4               | 0.0%  | 0.1%  | 0.0%  | 0.5%  | 0.4%  | 0.0%  | 0.0%  | 0.6%  |

| Total                     | 30.7% | 30.7% | 32.6% | 46.9% | 36.6% | 38.3% | 46.3% | 37.5% |

| Computational Times [sec] | 204.6 | 204.1 | 178.5 | 179.8 | 204.5 | 178.9 | 192.0 | 311.3 |

Table 1: Current W@R limits and different product mixes and volumes.

Table 2 presents the results obtained when the W@R limits change. We considered the same mixes and volumes of products shown in Table 1. We aim at calculating if the W@R limit targets were possible to achieved with the current inspection capacity. Let us focus again on Mix 4 and Mix 7. The total required capacity is similar (59.7% and 59.3%) and the balance of the workload on the inspection tools is also similar (32.7% to 31.7% for inspection tools of Type 1, 19.6% to 19.8% for inspection tools of Type 2 and 7.4% to 7.8% for inspection tools of Type 3) contrary to Table 1. As previously explained, this is mainly due to the new mix of products. But with these new limits, the frequencies of lots to sample have changed, and the inspection operations where lots are sampled are also different. This explains why the balance of the workload can change according to W@R Limits. Moreover, the results demonstrate the impact of the positions and the coverage of inspection operations in the product route. Concerning the Calculation time, it varies from 178 to 342 seconds. Since the time horizon corresponds to decisions at the tactical level (e.g., one month of production) the calculation time can be considered as reasonable.

| Inspection Tools          | Mix 1 | Mix 2 | Mix 3 | Mix 4 | Mix 5 | Mix 6 | Mix 7 | Mix 8 |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Tool Type 1               | 19.6% | 23.4% | 23.4% | 32.7% | 25.5% | 26.5% | 31.7% | 26.4% |

| Tool Type 2               | 11.5% | 9.2%  | 10.7% | 19.6% | 15.5% | 16.3% | 19.8% | 15.9% |

| Tool Type 3               | 7.4%  | 6.0%  | 6.6%  | 7.4%  | 5.7%  | 6.0%  | 7.8%  | 5.8%  |

| Tool Type 4               | 0.0%  | 0.0%  | 0.0%  | 0.0%  | 0.0%  | 0.0%  | 0.0%  | 0.0%  |

| Total                     | 38.5% | 38.6% | 40.7% | 59.7% | 46.6% | 48.8% | 59.3% | 48.1% |

| Computational Times [sec] | 342.5 | 320.0 | 303.3 | 298.4 | 306.3 | 283.5 | 311.1 | 314.7 |

Table 2: W@R target limits vs. Defect inspection capacity requirements and product mixes.

# 5 CONCLUDING REMARKS

Dynamic Sampling Strategies are very recent in literature, first works date from 2005 with the publication of Purdy et al. (2005). With the introduction of a Dynamic Sampling, the selection of lots to be inspected is done according to the production state. In consequence, the number of lots that will arrive to the defect inspection operations are not known in advance. For these reason, new methods to estimate the defect inspection capacity requirements are necessary. In this paper, a mathematical model was proposed in order to determine the defect inspection allocation requirements, when a Dynamic Sampling strategy is used. Key factors are taken into account such as W@R limits of process tools, mix and volume of products, product control plan (e.g., coverage, number and position of inspection operations) and qualification of process tools as well as inspection tools. Our model aims at anticipating the inspection capacity requirements when

W@R limits are changing. Since inspection operations and qualifications of inspection tools depend on the product, we studied how the change of the mix and volume of products impacts the inspection workload and W@R limits. Further research focuses on the integration of the distance between process operations and control operations. New research avenues have been highlighted concerning the control plan design in order to minimize W@R levels on tools.

### **ACKNOWLEDGMENTS**

This study has been done within the framework of a joint collaboration of STMicroelectronics in Rousset, France, and the Center of Microelectronics in Provence of the Ecole des Mines de Saint-Etienne in Gardanne, France.

#### REFERENCES

- Dauzère-Pérès, S., J.-L. Rouveyrol, C. Yugma, and P. Vialletelle. 2010. "A Smart Sampling Algorithm to Minimize Risk Dynamically". In *Proceedings of the 2010 IEEE/SEMI Advanced Semiconductor Manufacturing Conference*, 307–310.

- Gudmundsson, D. 2005. Inspection and Metrology Capacity Allocation in the Full Production and Ramp Phases of Semiconductor Manufacturing. Ph. D. thesis, University of California, Berkeley, USA.

- Hyung Joo Lee, B. 2008. *Advanced Process Control and Optimal Sampling in Semiconductor Manufacturing*. Ph. D. thesis, The University of Texas at Austin, USA.

- Johnzén, C., S. Dauzère-Pérès, and P. Vialletelle. 2011. "Flexibility Measures for Qualification Management in Wafer Fabs". *Production Planning & Control* 22 (1): 81–90.

- May, G. S., and C. J. Spanos. 2006. "Fundamentals of Semiconductor Manufacturing and Process Control". John Wiley & Sons.

- Nduhura Munga, J., S. Dauzère-Pérès, P. Vialletelle, and C. Yugma. 2011. "Dynamic Management of Controls in Semiconductor Manufacturing". In *Proceedings of the 22nd Annual IEEE/SEMI Advanced Semiconductor Manufacturing Conference*, 18–23.

- Nduhura Munga, J., S. Dauzère-Pérès, C. Yugma, and P. Vialletelle. 2011. "A Mathematical Programming Approach for Determining Control Plans in Semiconductor Manufacturing". In *Proceedings of the International Conference on Industrial Engineering and Systems Management*, 9 pages.

- Nduhura Munga, J., G. Rodriguez-Verjan, S. Dauzère-Pérès, C. Yugma, P. Vialletelle, and J. Pinaton. 2012. "Literature Review on Sampling Techniques in Semiconductor Manufacturing". In *Working Paper, submitted*.

- Nurani, R. K., R. Akella, A. J. Strojwas, R. Wallace, M. G. McIntyre, J. Shields, and I. Emami. 1994. "Development of an Optimal Sampling Strategy for Wafer Inspection". In *Proceedings of the 1994 International Symposium on Semiconductor Manufacturing*, 143–146.

- Purdy, M., C. Nicksic, and K. Lensing. 2005. "Method for Efficiently Managing Metrology Queues". In *Proceedings of the 2005 IEEE International Symposium on Semiconductor Manufacturing*, 71–74.

- Rodriguez-Verjan, G. L., S. Dauzère-Pérès, and J. Pinaton. 2011, December. "Impact of Control Plan Design on Tool Risk Management: A Simulation Study in Semiconductor Manufacturing". In *Proceedings of the 2011 Winter Simulation Conference*, edited by S. Jain, R. R. Creasey, J. Himmelspach, K. P. White, and M. Fu, 1918–1925. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Song-bor, L., R. L. Ta-Yung, L. Janson, and C. Yu-Ching. 2003. "A Capacity-Dependence Dynamic Sampling Strategy". In *Proceedings of the 2003 IEEE International Symposium on Semiconductor Manufacturing*, 312–314.

- Tirkel, I., N. Reshef, and G. Rabinowitz. 2009. "In-Line Inspection Impact on Cycle Time and Yield". *IEEE Transactions on Semiconductor Manufacturing* 22 (4): 491–498.

#### **AUTHOR BIOGRAPHIES**

GLORIA LUZ RODRIGUEZ VERJAN studied industrial engineering at the University Javeriana, Bogotá, Colombia, and obtained her MSc degree in industrial engineering from the Ecole des Mines de Saint-Etienne, France. She is currently working as Research Engineer at a Franco-Italian semiconductor manufacturer, and working towards a doctoral degree within the Center of Microelectronics in Provence (CMP) of the Ecole des Mines de Saint-Etienne. From 2006 to 2009 she worked as logistics analyst at P&A Renault located in Bogotá, Colombia. She has also been part-time lecturer in simulation at the Ecole des Mines de Saint-Etienne in France, Sabana University and Javeriana University in Colombia. Her research work has been focused in simulation and logistics operations, and most recently in optimization of semiconductor manufacturing operations. Her email address is rodriguez@emse.fr or gloria.rodriguez@st.com.

STÉPHANE DAUZÈRE-PÉRÈS is Professor at the Center of Microelectronics in Provence of the Ecole des Mines de Saint-Etienne, where he is heading the Manufacturing Sciences and Logistics Department. He received the Ph.D. degree from the Paul Sabatier University in Toulouse, France, in 1992; and his Habilitation Diriger des Recherches from the Pierre and Marie Curie University, Paris, France, in 1998. He was a PostDoc Fellow at the Massachusetts Institute of Technology U.S.A., in 1992 and 1993, and Research Scientist at Erasmus University Rotterdam, The Netherlands, in 1994. He has been Associate Professor and Professor from 1994 to 2004 at the Ecole des Mines de Nantes in France. He was invited Professor at the Norwegian School of Economics and Business Administration, Bergen, Norway, in 1999. Since March 2004, he is Professor at the Ecole des Mines de Saint-Etienne. His research mostly focuses on optimization in production and logistics, with applications in planning, scheduling, distribution and transportation. He has published more than 40 papers in international journals and 100 communications in conferences. His email address is dauzere-peres@emse.fr.

**JACQUES PINATON** is manager of Process Control System group at ST Microelectronics Rousset, France. He is an engineer in metallurgy from the Conservatoire National des Arts et metiers dAix en Provence. He joined ST in 1984. After 5 years in the process engineering group, he joined the device department to implement SPC and Process Control methodology and tools. He participated in the start up of 3 generations of fabs. He is leading various Rousset R&D programs on manufacturing science including programs on automation, APC, and diagnostics. His email address is jacques.pinaton@st.com.